## 3.3 L'additionneur binaire

Il s'agit d'un circuit logique qui fait une opération arithmétique. Tout comme une addition en décimale, l'addition du premier rang c.-à-d. de 2<sup>0</sup> ne nécessite pas de connaître la retenue du rang précédent puisqu'il y en pas.

Soient deux nombres A et B sur trois bits chacun :  $A=a_2a_1a_0$  et  $B=b_2b_1b_0$  :

## 3.3.1 Le demi-additionneur

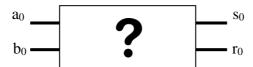

L'addition entre  $a_0$  et  $b_0$  se fait avec un circuit combinatoire logique qui a deux entrées uniquement et deux sorties :  $s_0$  la somme et  $r_0$  la retenue. Une fois ce circuit défini, par ses entrées et leurs nombre et ses sorties et leurs nombre, on établie la TdV.

Fig. 3.1 Circuit demi-additionneur

| $a_0$ | $b_0$ | S <sub>0</sub> | $r_0$ |

|-------|-------|----------------|-------|

| 0     | 0     | 0              | 0     |

| 0     | 1     | 1              | 0     |

| 1     | 0     | 1              | 0     |

| 1     | 1     | 0              | 1     |

Tab.1 TdV du demi-additionneur

Sur la colonne de la somme,  $s_0$  prend 1 quand il y a 0+1=1 ou bien 1+0=1.

Sur la colonne de la retenue,  $r_0$  prend 1 quand il y a  $1+1=2_{10}=(10)_2$ . Le zéro correspond à la somme  $s_0$  et le 1 à la retenue  $r_0$ .

Cette TdV possède deux sorties, donc fonctions différentes. L'expression algébrique de ces deux fonctions sont tirées de la TdV sans avoir à les simplifier par TK car il n y a pas de <u>1</u> adjacents.

$$s_0 = \overline{a}_0 \cdot b_0 + a_0 \cdot \overline{b}_0 = a_0 \oplus b_0$$

$$r_0 = a_0 \cdot b_0$$

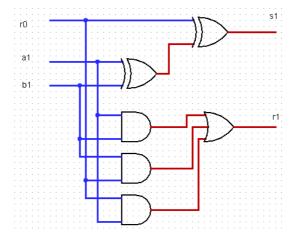

Fig 3.2 Circuit demi-additionneur

## 3.3.2 L'additionneur complet

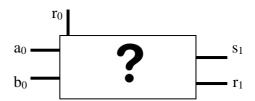

Il s'agit maintenant d'additionner  $a_1$  à  $b_1$  mais avec une information supplémentaire qui est  $r_0$ . Le circuit combinatoire possède toujours 2 sorties la somme  $s_1$  et la retenue  $r_1$ , mais trois entrées  $a_1$ ,  $b_1$  et  $r_0$ : c'est l'additionneur du  $2^{\text{ieme}}$  rang ( $2^1$ ). C'est l'additionneur du  $2^{\text{ieme}}$  rang ( $2^1$ ). Il est complet car par rapport au demi-additionneur, celui-ci tient compte de la retenue provoquée à l'étage (rang) précédent.

Traçons la TdV de ces 2 sorties :

| $a_1$ | $b_1$ | $\mathbf{r}_0$ | $s_1$ | $\mathbf{r}_1$ |

|-------|-------|----------------|-------|----------------|

| 0     | 0     | 0              | 0     | 0              |

| 0     | 0     | 1              | 1     | 0              |

| 0     | 1     | 0              | 1     | 0              |

| 0     | 1     | 1              | 0     | 1              |

| 1     | 0     | 0              | 1     | 0              |

| 1     | 0     | 1              | 0     | 1              |

| 1     | 1     | 0              | 0     | 1              |

| 1     | 1     | 1              | 1     | 1              |

Fig. 3.3 Circuit additionneur Complet

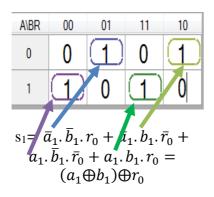

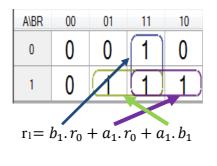

Sur le TK de  $s_1$ , il n'y a aucun  $\underline{1}$  adjacent. L'expression de  $s_1$  conduit donc à une forme canonique, avec  $A=a_1$ ,  $B=b_1$  et  $R=r_0$ . Pour  $r_1$ , il existe trois groupes de deux  $\underline{1}$  adjacents.

Fig 3.4 Circuit Additionneur Complet

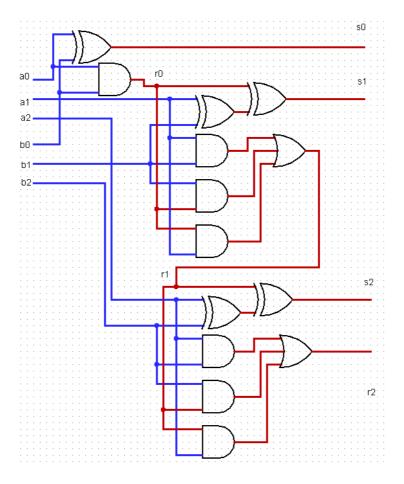

## 3.3.3 L'additionneur 3bits

Ce circuit doit donc effectuer une addition de deux nombres sur trois bits chacun comme suit :

| $2^3$           | $2^{2}$               | $2^{1}$        | $2^{0}$        |

|-----------------|-----------------------|----------------|----------------|

| r <sub>2</sub>  | $\mathbf{r}_1$        | r <sub>0</sub> |                |

| +               | $a_2$                 | $a_1$          | $a_0$          |

| +               | <b>b</b> <sub>2</sub> | b <sub>1</sub> | $b_0$          |

| =s <sub>3</sub> | S2                    | S <sub>1</sub> | S <sub>0</sub> |

| $2^3$ | $2^2$ | $2^{1}$ | $2^{0}$ |

|-------|-------|---------|---------|

| 1     | 1     | 1       |         |

| +     | 1     | 1       | 1       |

| +     | 1     | 1       | 1       |

| =1    | 1     | 1       | 0       |

| $2^3$ | $2^2$ | 21 | $2^{0}$ |

|-------|-------|----|---------|

| 0     | 0     | 0  |         |

| +     | 0     | 1  | 1       |

| +     | 1     | 0  | 0       |

| =1    | 1     | 1  | 1       |

L'opération se fait sur quatre étages ou rangs, les trois premiers sont ceux des opérandes et le dernier, né de la retenue.

Le tableau du milieu et de droite montrent deux exemples d'addition binaire. Le premier  $(7)_{10} + (7)_{10} = (14)_{10}$  et le second  $(3)_{10} + (4)_{10} = (7)_{10}$

Fig 3.5 Circuit Additionneur 3bits

On voit bien que pour le premier rang :  $2^0$ , le circuit ne doit avoir que deux entrées  $a_0$  et  $b_0$  pour ne donner que  $d_0$  et  $r_0$  c'est le demi-additionneur. Pour tous les rangs supérieurs  $2^1, 2^2$  ...etc. l'opération se fait avec le même circuit logique, il suffit juste de modifier les entrées. Cela se fait avec l'additionneur complet.